Bloque que genera una señal PWM con un cierto número de pulsos en la salida digital DO9, respetando una rampa de subida y caída en la frecuencia.

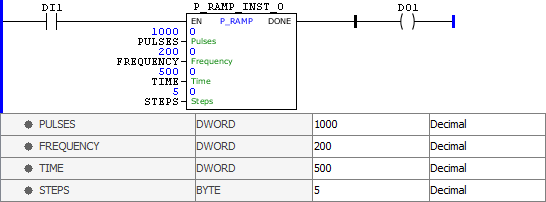

Representación Ladder

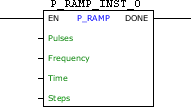

Estructura del Bloque

Tipo de Variable |

Nombre |

Tipo de Dato |

Descripción |

VAR_INPUT |

EN |

BOOL |

Habilitación del bloque |

Pulses |

DWORD UDINT |

Número de pulsos total de la ejecución del bloque |

|

Frequency |

DWORD UDINT |

Frecuencia máxima que se desea alcanzar |

|

Time |

DWORD UDINT |

Tiempo de rampa [ms] |

|

Steps |

BYTE USINT |

Pasos de incremento de frecuencia |

|

VAR_OUTPUT |

DONE |

BOOL |

Habilitación de salida |

VAR |

P_RAMP_INST_0 |

P_RAMP |

Instancia de acceso a la estructura del bloque |

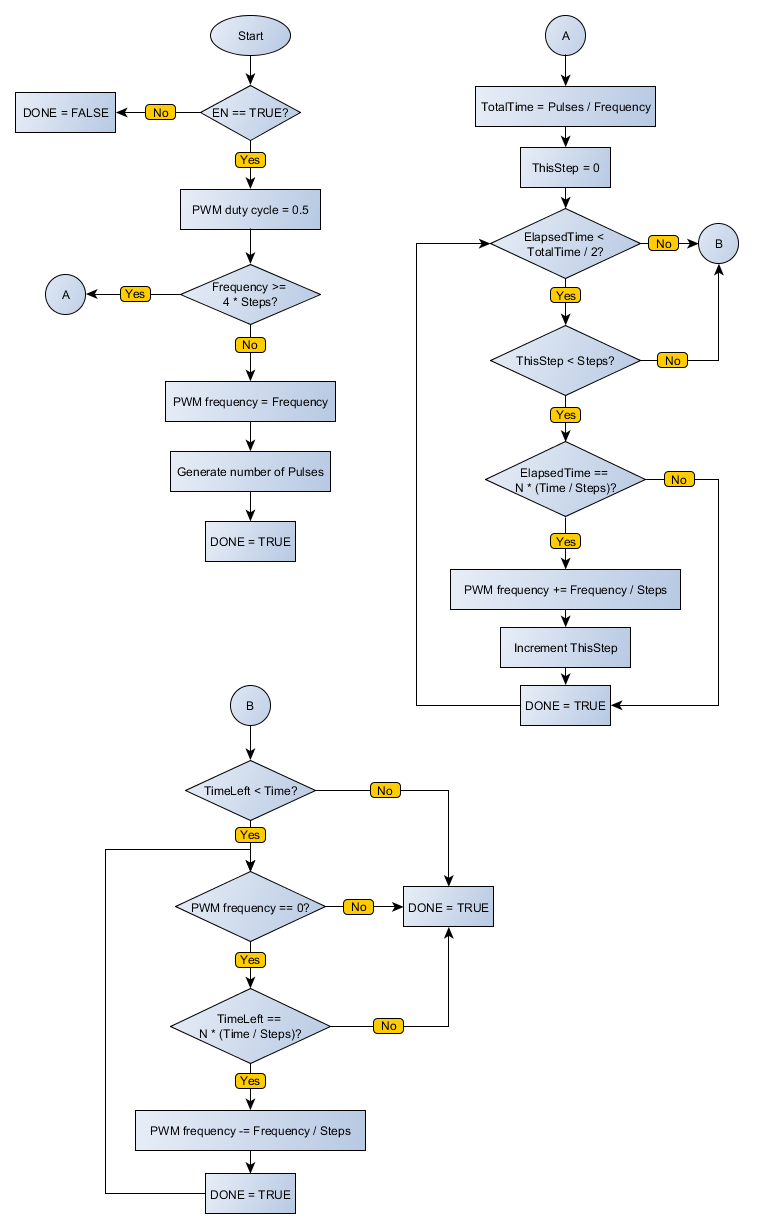

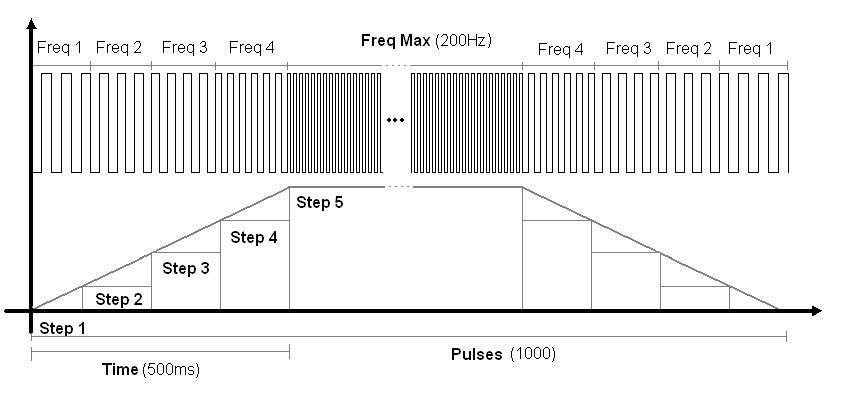

Operación

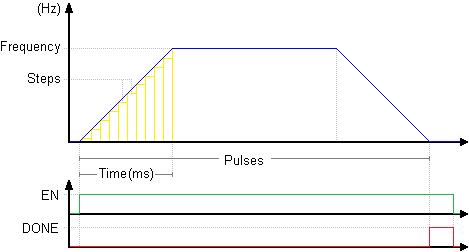

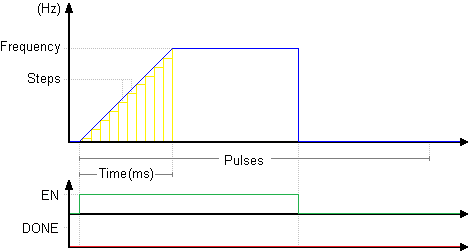

Cuando la entrada EN es TRUE, el bloque genera una señal PWM en la salida DO9. Inicialmente, genera una rampa de subida, que va desde la frecuencia cero hasta el valor de Frequency (entre 0 y 200 KHz), según los ajustes de Time y Steps. En el momento adecuado, el bloque genera una rampa de descenso, con el mismo perfil que la rampa de subida, hasta que la frecuencia es cero y se alcanza el valor de los pulsos.

Cuando se alcanza el valor de los Pulses, la salida DONE pasa a TRUE.

Si la entrada EN va a FALSE antes de alcanzar el número de Pulses, la generación de PWM se detiene inmediatamente.

El ciclo de trabajo de la señal permanece constante a 0.5 a través de la ejecución del bloque.

Para lo que se genera la rampa de frecuencia, es necesario que el número de Steps sea menor o igual a un cuarto del valor de Frequency, es decir:

Steps ≤ (1/4). Frequency

Si no se respeta esta limitación, no se generará la rampa de frecuencia. Significa que la señal PWM va directamente al valor de Frequency.

Ejemplo: Si el valor de Frequency es 100 Hz, para que se genere la rampa de frecuencia, el número de Steps debe ser menor o igual a 25.

|

¡NOTA! Habiendo otros bloques PWM en ejecución, tendrá prioridad aquel que sea llamado primero. |

|

¡NOTA! Este bloque tiene prioridad sobre cualquier bobina que esté escribiendo datos en DO9. |

Compatibilidad

Equipo |

Versión |

PLC300 |

2.00 o superior |

Diagrama de Flujo del Bloque

Ejemplo en Ladder

El ejemplo de arriba habilita una señal PWM en la salida DO9 con frecuencia inicial de 0 Hz y duty cycle de 50%. El tiempo de la rampa de subida de frecuencia es de 500 ms, y la rampa tiene 5 pasos de frecuencia (0, 50, 100, 150 y 200 Hz). En el total de la ejecución del bloque serán enviados a la salida 1000 pulsos. Finalizado el bloque exitosamente, la salida Q es activada.

Ejemplo en ST

El siguiente ejemplo muestra las instrucciones para aplicar el ejemplo anterior en el lenguaje ST.

VAR PULSES : DWORD := 1000; FREQUENCY : DWORD := 200; TIME : DWORD := 500; STEPS : BYTE := 5; P_RAMP_INST_0 : FB_P_RAMP; END_VAR

P_RAMP_INST_0.EN := DI1; P_RAMP_INST_0( Pulses:=PULSES, Frequency:=FREQUENCY, Time:=TIME, Steps:=STEPS); DO1 := P_RAMP_INST_0.DONE;

|

|---|